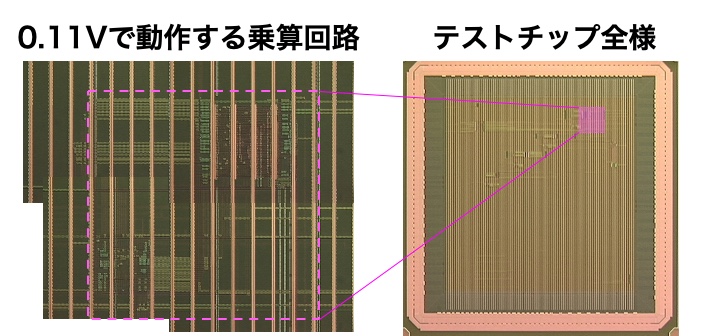

動作時のチップの消費電力は電源電圧の2乗で変化するため、消費電力を小さくするには電源電圧を下げるのが非常に有効です。電源電圧を下げると動作速度が遅くなるという難点がありますが、センサーノードや医療用デバイスに使われるチップでは、さほどの高速性は要求されず、消費エネルギーを極力小さくすることが最優先されます。こういったデバイスでは、通常のチップで使われる電源電圧(例えば65nmプロセスのデバイスなら1.2V等)ではなく、もっと低い電源電圧で動作させて、省電力を狙います。学部の集積回路工学の授業では、「スイッチ素子(MOSトランジスタ)にはしきい値電圧(Vt)があり、素子のゲートにVt以上の電圧を印加するとスイッチがオンして回路が動作する」と教わりますが、超低電圧回路ではVt以下の電圧で動作させます。どのMOSトランジスタもオンせず、オフ状態でリーク電流(もれ電流)だけで論理動作を行います。これを実現するには設計段階で様々な工夫が必要ですが、宇佐美研では超低電圧に向けた技術を駆使して16ビット乗算回路を設計し、65nmSOTBという製造プロセスを使ってテストチップを試作しました(図)。

試作チップを実測したところ、0.11Vまで正しく乗算結果が得られることが観測できました。さらに、消費エネルギーは電源電圧を低くすればするほど小さくなるのではなく、0.3V付近で消費エネルギーが最小になることも明らかになりました(下図)。この論文は、イタリアで開催された国際学会EUROSOI-ULIS 2015にアクセプトされ、発表しました。

なお、宇佐美教授による「超低電圧LSIの設計技術」に関する解説記事が、下記に掲載されています。興味のある方はぜひご参照ください。