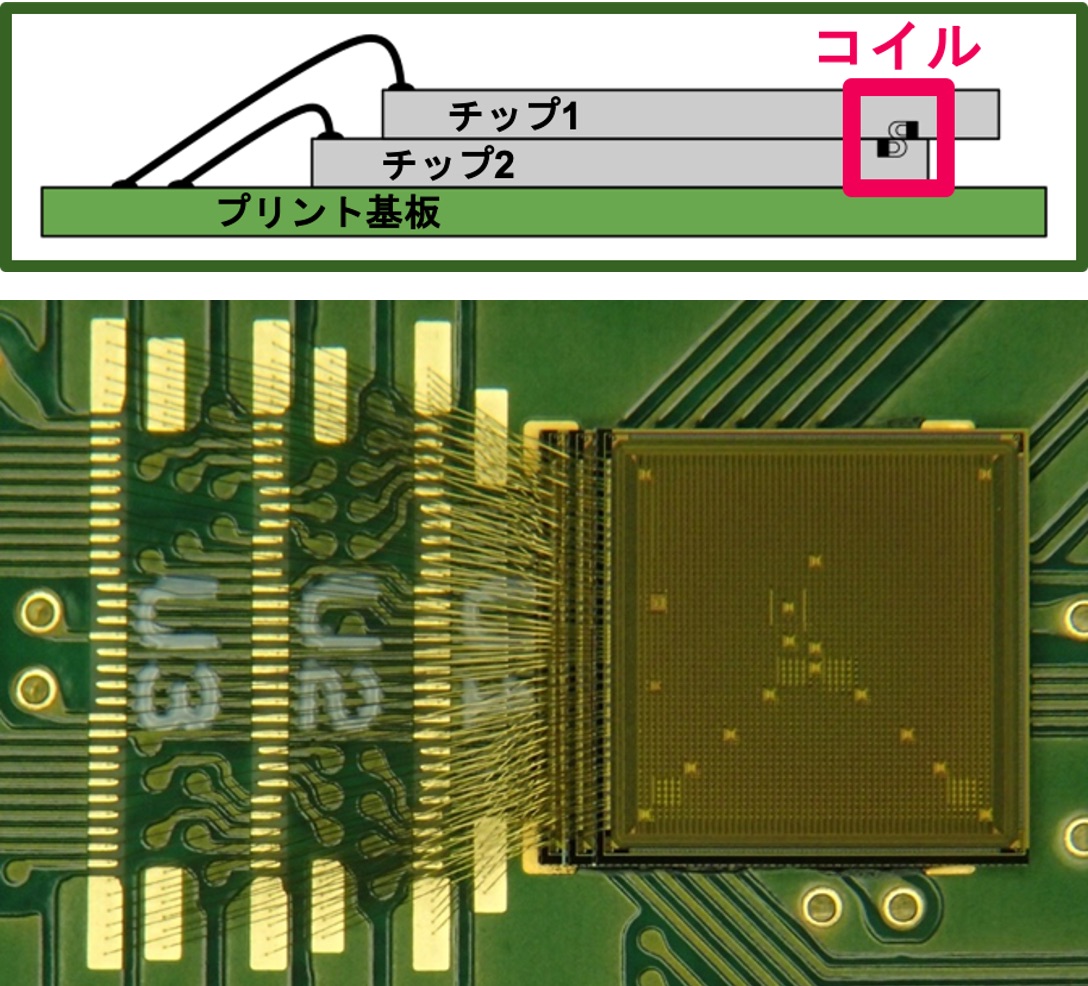

素子の微細化には膨大な開発・製造コストがかかること、また、微細化に物理的な限界が見え始めてきたことから、すべての機能を1チップに詰め込むのではなく複数のチップで実現し、3次元積層して使う技術が注目を浴びています。3次元積層したチップ間でどのように信号をやり取りするかは大きな課題であり、現在ではチップに垂直方向に穴をあけ金属を埋め込んで接続するTSV(Through Silicon VIA)という技術が主流です。ところが、TSVには歩留りや製造コストの課題があるため、宇佐美研究室では慶応大、東大他との共同研究により、チップ間を無線通信する方式を使った3次元積層チップの設計技術について、研究を進めています。とくに、3次元積層した場合のチップの発熱対策と温度制御は重要な研究課題です。チップは動作中に電力消費して発熱しますが、3次元積層した場合、放熱経路やチップの温度上昇の特性が、積層しない場合と異なる可能性があるためです。宇佐美研では、これを実測するための専用チップを設計・試作して、3枚のチップを3次元積層しました(図)。

積層チップを実測した結果、どの段のチップで発熱したかにより, チップ温度が20℃も異なること、また、発熱後わずか40ミリ秒でチップ温度が20℃も上昇する、という知見が得られました。この成果は、2019年2月に電子情報通信学会 VLSI設計技術研究会で発表しています。現在、この知見を活かしつつ、チップ上に細かく配置した温度センサ回路で温度をモニタリングし、最適な温度制御を行う技術の研究を進めています。